# **OML Sync Ctrl**

#### For Fun And Science

### **OML Sync Control**

- What is it

- How can it be tested

- How is it implemented

- What can we do about that?

### What is it?

- OML: OpenML.

- Like EXT Swap Control, but better

- Can schedule buffer swaps and get feedback

- Use case: Neuroscience

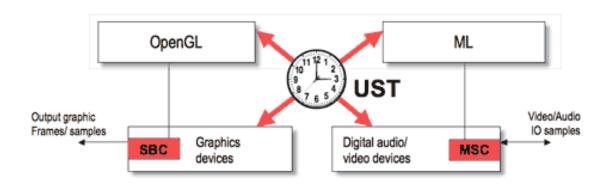

### UST, MSC, and SBC

**UST:** Common time base

MSC: Number of vsyncs

SBC: Number of buffer swaps

#### **Functions**

- glXGetSyncValuesOML

- gIXGetMscRateOML

- glXSwapBuffersMscOML(target, div, rem)

- glXWaitForMscOML(target, div, rem)

- glXWaitForSbcOML(target)

## Things you will get wrong

- Divisor 0

- INT64 wrap

- Returning 0 values

- GetSyncValues scheduling

- Externally meaningless values

- Timestamps from the future!

#### **Assertions to test**

SBC starts at 0

Counters don't go backwards after glxWaitFor\*

SwapBuffers schedules correct SBC

Requested target MSC/SBC was hit

Divisor and remainder respected

Spurious SBC increments

#### **Statistics**

Suspicious:

stddev ( $\Delta$ UST /  $\Delta$ MSC) > 100UST?

Broken:

stddev ( $\Delta t / \Delta MSC$ ) > 1ms?

|  $avg(\Delta t / \Delta MSC)$  - 1s / GetMSCRate | > 50us?

### Static analysis

```

if (__builtin_constant_p(frame) || (__builtin_constant_p(tv_sec) &&

static int already warned; \

+

if (! already warned) { \

_already_warned = 1; \

+

DRI2WarnConstantUSTOrMSC(__FILE__, __LINE__, __func__,

+

pDraw, frame, tv_sec, tv_usec); \

```

### Performance in the wild

intel\_dri.c: In function 'I830DRI2ScheduleFlip':

intel\_dri.c:956:273: warning: call to '\_DRI2WarnConstantUSTOrMSC' declared with attribute warning: UST and MSC can't be constants. Please fix this driver's DRI2 support for OML sync control.

intel\_dri.c: In function 'I830DRI2ScheduleWaitMSC':

intel\_dri.c:1554:282: warning: call to '\_DRI2WarnConstantUSTOrMSC' declared with attribute warning: UST and MSC can't be constants. Please fix this driver's DRI2 support for OML\_sync\_control.

intel\_dri.c: In function 'I830DRI2ScheduleSwap':

intel\_dri.c:1369:273: warning: call to '\_DRI2WarnConstantUSTOrMSC' declared with attribute warning: UST and MSC can't be constants. Please fix this driver's DRI2 support for OML\_sync\_control.

#### Performance in the wild

#### Until xf86-video-intel commit 2.99.912~134:

sna\_dri2.c: In function 'sna\_dri2\_schedule\_wait\_msc':

sna\_dri2.c:2478:282: warning: call to '\_DRI2WarnConstantUSTOrMSC' declared with attribute warning: UST and MSC can't be constants. Please fix this driver's DRI2 support for OML\_sync\_control.

sna\_dri2.c: In function 'sna\_dri2\_immediate\_blit':

sna\_dri2.c:1548:277: warning: call to '\_DRI2WarnConstantUSTOrMSC' declared with attribute warning: UST and MSC can't be constants. Please fix this driver's DRI2 support for OML\_sync\_control.

sna\_dri2.c:1564:275: warning: call to '\_DRI2WarnConstantUSTOrMSC' declared with attribute warning: UST and MSC can't be constants. Please fix this driver's DRI2 support for OML\_sync\_control.

sna dri2.c: In function 'chain flip':

sna\_dri2.c:1731:281: warning: call to '\_DRI2WarnConstantUSTOrMSC' declared with attribute warning: UST and MSC can't be constants. Please fix this driver's DRI2 support for OML\_sync\_control.

In function 'sna\_dri2\_schedule\_flip',

inlined from 'sna\_dri2\_schedule\_swap' at sna\_dri2.c:2214:6:

sna\_dri2.c:2034:276: warning: call to '\_DRI2WarnConstantUSTOrMSC' declared with attribute warning: UST and MSC can't be constants. Please fix this driver's DRI2 support for OML\_sync\_control.

sna\_dri2.c: In function 'sna\_dri2\_schedule\_swap':

sna\_dri2.c:2324:273: warning: call to '\_DRI2WarnConstantUSTOrMSC' declared with attribute warning: UST and MSC can't be constants. Please fix this driver's DRI2 support for OML\_sync\_control.

## Piglit results

### Where to go from here?

Driver patches

Glamor-EGL? video-modesetting?

### Questions, Discussion?